大容量NAND颗粒背后的秘密

喜欢数码设备的朋友们都对闪存产品的价格跳水印象颇深,记得10年前我们买一个32MB的闪盘,需要几百元,而现在购买一个16GB的闪盘连200元都不到。短短几年的时间,花同样多的钱我们可以买到500倍的容量,而同时期的硬盘容量也仅仅增加了几十倍而已(

喜欢数码设备的朋友们都对闪存产品的价格跳水印象颇深,记得10年前我们买一个32MB的闪盘,需要几百元,而现在购买一个16GB的闪盘连200元都不到。短短几年的时间,花同样多的钱我们可以买到500倍的容量,而同时期的硬盘容量也仅仅增加了几十倍而已(

40GB→2TB)。前不久,三星半导体发布了使用9层晶圆堆叠技术的32GB

MicroSD卡,同时登场亮相的还有采用

17层晶圆堆叠技术的64GB MoviNAND闪存芯片,再次刷新了业界纪录。这么多年来,是什么技术让NAND闪存的容量和速度呈指数提高呢?工艺、封装还是其它不为我们所知的新技术?就请跟随本文一起解密闪存革命式发展之路吧!

初期竞争:NAND Flash的胜出

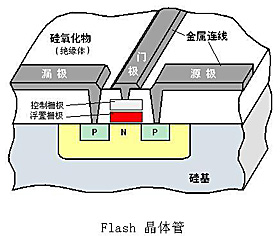

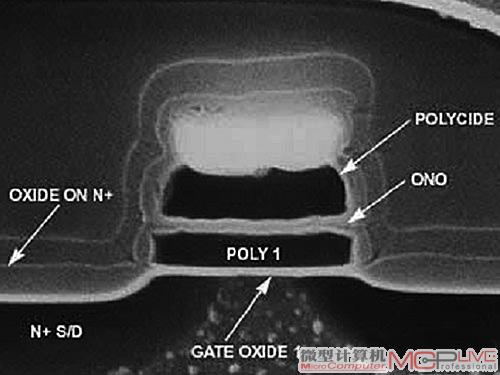

闪存,英文名称叫做Flash Memory,顾名思义,闪存能够像闪电一样在瞬间完成数据存储工作。下面就是闪存芯片中使用的晶体管和CPU中使用的晶体管对比图。

闪存芯片中的晶体管单元(左)与CPU中的晶体管单元(右)

从图中,细心的朋友会发现闪存的晶体管比CPU的晶体管多一个浮置栅极,我们又把它叫做“浮栅”,这就是闪存存储数据的基本单元。读取闪存中的数据时,电路通过检测浮栅的微弱电压来判断内部是否有电荷,从而得到相应“0”或者“1”数据;写入数据时,由于浮栅周围是绝缘体(比如二氧化硅),必须在相对高的电压下先擦除其中全部内容,然后再通过热电子注入或者隧道效应这种非导体接触方式,向浮栅中充入电荷完成写入。浮栅这种特殊结构,使闪存具有在掉电的情况下也能长期保存数据的优势;但与此同时,由于写入数据前必须先擦除数据,而导致闪存写入速度始终无法赶上内存。

在闪存诞生初期,工程师们使用内存一样的寻址方式去存取Flash,这就是初的NOR Flash。这种寻址方式可以方便地调用任意bit位的浮栅数据。但很快工程师们就发现内存寻址虽然可以方便地读取每一位,但是由于Flash写入的复杂流程,导致写入速度极慢。而且内存寻址地址线和数据线分开,每次容量升级都需要增加地址线数量,这对于未来单颗芯片容量的提升很不利,系统的兼容性无法得到保障。

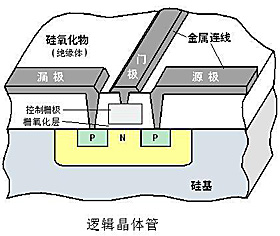

NAND闪存的页面结构

在这种背景下,工程师们使用了新的寻址方式:在闪存内部将晶体管串联起来,外部接口共用数据线、地址线和控制线,这就是后来的NAND Flash。这样一来,同一家公司生产的NAND Flash从128MB到8GB的颗粒能够保持引脚兼容,极大的方便了硬件系统设计。

追求容量,大兴土木搞地产

在确定了内部结构和外部接口后,NAND Flash便进入了快速发展期,用迅速提高容量和性能的方式来抢占市场。要达成这一目标,我们首先需要改进的便是生产工艺。

◆工艺升级:NAND Flash的助推剂

要让闪存能够存入更多的数据,就需要在内部放置更多的浮栅晶体管。这个道理非常简单,但是鉴于终用于芯片产品中的晶片(晶圆切割后的裸片,也就是Die)只有那么大,于是我们只能在晶片上频繁地进行“旧城改造”工作,使单位面积内能够装下更多的晶体管。在这种指导思想下,Flash的制造工艺迅速从250nm(128MB)发展到90nm(2GB)、直到现在的30nm生产工艺,从技术角度来看,NAND颗粒的生产工艺始终领先同时代CPU生产工艺一个身位。

闪存颗粒的生产工艺与CPU非常相似

现在GB级的闪盘也许已经能够满足大多数人的需求,但正好像在2GB的闪盘中很少有厂商使用2枚1GB的芯片,更多的存储设备都只对单颗大容量的芯片更感兴趣。随着智能手机、数码相机技术的迅速发展,市场对大容量存储芯片的要求也越来越高,而且这种趋势正变得愈发迫切。特别是存储设备缩小之后,例如现在的MicroSD卡,对闪存颗粒的要求越来越高,传统的“旧城改造”已经跟不上时代发展的要求,这就催生了存储概念的升级换代。

◆MLC:存储概念升级的“歪脑筋”

消费者对于闪存容量的贪欲,让工程师们开始动起“歪脑筋”,那就是改变浮栅职能,让每个浮栅可以存入更多的信息数据。

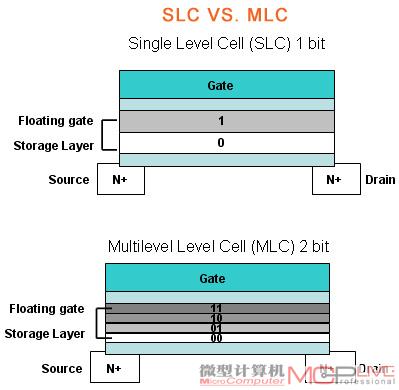

早的浮栅跟内存芯片中的基本存储单元一样,只能一个单元记录一个“0”或者“1”,这样的Flash芯片被称作单层式存储(Single Level Cell,简称为SLC)。经过对浮栅存储电荷数量以及读取电压的研究,工程师试着让改进之后的浮栅晶体管有选择性的存入不同数量的电荷,并在读取时表现出不同的电压值,这样一个单元就可以记录下四种不同的状态,分别为“00”、“01”、“10”以及“11”。这样一来,在利用现有生产线产能,且不需要增加多少成本的情况下将闪存容量增加一倍。这便是多层式存储闪存(Multi Level Cell,简称为MLC)。

SLC与MLC之间的差异

目前业界极端的MLC存储颗粒已经开始考虑引入3位8状态的读写,也就是同样一个记录单元,可以记录“000”、“001”、“010”、“011”、“100”、“101”、“110”以及“111”—这相当于在之前MLC的基础上再将容量提升1倍。

MLC技术的广泛应用虽然暂时缓解了普通用户对容量的要求,但好景不长,固态硬盘的到来让NAND颗粒再一次陷入困惑中—因为固态硬盘需要提供上百GB的容量以及超越普通硬盘的读写性能,且价格还不能太高。而另一方面,短期内制造工艺方面已经没有更大的潜力可挖了,这要怎么办呢?工程师开始在芯片集成上打主意了……

◆堆叠:芯片中的摩天大楼

在芯片产业的初级阶段,一颗封装好的芯片往往只会包含一颗晶片;如果系统需要复杂的功能,将多颗芯片集成在电路板上就可以了。但移动设备和微型存储设备的需求很特殊,需要在极其有限的空间内实现大容量,于是工程师们必须认真考虑多芯片封装的可能性(Multi Chip Package,MCP)。

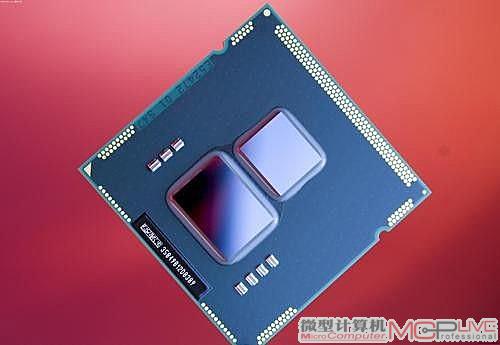

目前,多芯片封装技术中使用多的仍然是平行排列的MCP,如英特尔第一代双核处理器Pentium D,以及新的Core i5处理器(CPU单元+IGP单元)。但平行的MCP会显著增加芯片成品的面积,这对于Flash工业来说并不现实,于是垂直MCP就成了好的解决方案。

Core i3处理器便是典型的平行封装

简单来讲,垂直MCP技术就是将多片晶圆通过粘合剂垂直粘在一起,并通过导线让他们互相接通,后才将粘合在一起的Die们封装成一个芯片。这样就可以在较小的面积内实现更多的功能或者存储容量,弥补芯片制造工艺上的不足。随着垂直MCP技术的日趋成熟,我们在文章开头提到的32GB MicroSD和64GB NAND芯片终于诞生了。

其中在32GB的Micro SD卡中,工程师将8片NAND Flash晶片和1片控制器垂直封装在一起,同时达到了MicroSD卡1mm厚度的要求。在对厚度要求不是很明显的场合,三星更是将16片NAND Flash晶片和一片控制器垂直封装在一起,组成64GB的海量空间。如果使用这种芯片,很多上网本可能只需要一颗NAND颗粒就可以满足存储容量的需求了。

荣耀背后的艰辛:技术进步犹如蜀道难

虽然我们看到综合应用各种方法之后,NAND颗粒的存储空间近些年来迅速增加,但其中的艰辛却不为世人所知,技术的每一小步进步,背后往往需要付出巨大代价,可谓“蜀道难,难于上青天”。

◆用新工艺升级提高集成度

这不是简单的一句话,工艺升级背后需要成千上万名工程师的支持和数十亿美元的投入。例如英特尔研发32nm制程工艺的花费为6亿~9亿美元,而且在两年内还将为4条采用32nm制程的生产线继续投入70亿美元。

NAND颗粒基本上被少数几家大厂垄断

NAND闪存的生产也存在类似情况,Flash成本与工艺的联系十分紧密,如果不紧跟业界潮流、不断提升工艺、降低成本,就很容易陷入生产越多、亏损越大的恶性怪圈,这也是为什么目前业内有数以千计的生产闪存周边产品的公司,但核心的闪存生产却几乎被三星和东芝等几家大厂所垄断。

◆难以驯服的MLC

曾经在一段时间里,MLC被视为快速提高Flash容量的法宝。毕竟简单地微调生产线,重新设计Flash控制器就能成倍的提高Flash容量。但是MLC的工作原理决定了其性能和寿命无法与传统的SLC相比。

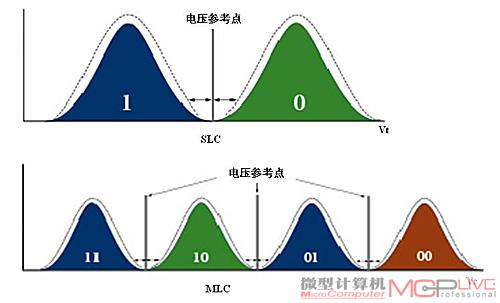

SLC和MLC读取电压的示意图

从图中我们可以看到,SLC仅有1个数值电压参考点,所以控制器能够很快地判定浮栅晶体管的状态是0还是1。但在MLC的机构中,存储四种状态就意味着需要三个电压参考点。为了保证电压区间的股沟宽度足以让控制器读取数值,那么MLC的工作电压势必要大于SLC,于是就造成了三个弊端:

A.更大电压跨度使得MLC写入和读取速度受到很大影响,因为更高的电压需要注入更多电荷,而这是需要时间的;

B.更高的工作电压极大地损害了浮栅的稳定性,使得MLC闪存的寿命只能达到SLC的十分之一;

C.为了保证数据写入读取的正确性,必须在写入前和读出后进行复杂的CRC数据校验工作,这样更进一步降低了MLC的读写性能。

即便到目前为止,MLC仍然不能脱掉“低能廉价”的帽子,在需要性能和稳定性的场合,如英特尔生产的企业级固态硬盘X25-E中始终坚持使用SLC Flash芯片。与之形成鲜明对比的是,3bit 8数据位的MLC还没有大规模推广就爆出稳定性问题,不得不尴尬返厂。

◆“高处不胜寒”

或许大家觉得盖个3~5层的“小洋楼”很容易,随便找几个懂点技术的工匠就行了。但如果是几十层的楼房呢?在微观的世界里,“盖楼”也不是非常容易的事情。而NAND颗粒的特性要求它能够拥有极高的稳定性,即便是遇到“地震”、“海啸”时仍能屹立不倒,保证数据安全。

首当其冲的便是芯片成品的厚度。以我们常用的MicroSD存储卡为例,这种产品的厚度为1mm,除开PCB基板、模具的厚度,留给晶片的厚度不到500μm(即0.5mm)。而传统的12英寸(直径300mm)晶圆切割厚度在80μm,粘合晶片的粘合剂厚度也要60μm,加上必要的Flash控制器,我们只能完成4层堆叠的MCP产品,效果不甚理想。为此,工程师们开始改进生产和封装工艺,抛弃切割极限80μm的晶圆锯,而使用更加先进的激光切割技术,成功地将晶圆厚度降低到30μm;与此同时改进粘合剂配方,在保证粘合性能和坚固的前提下将粘合层厚度降低到20μm,这样在MicroSD卡有限的空间里就堆叠多9层晶片。

多层堆叠的方式

其次要考虑的问题是如何散热,由于至今未能找到可靠的垂直MCP散热方式,这样高密度的堆叠MCP技术目前只能使用在发热不高的Flash存储上。当将多层高速逻辑芯片(如计算核心、接口控制器等)堆叠封装起来后,多个芯片工作发出的热量会在狭小的空间内快速积聚,极大的影响芯片稳定工作,同时由于粘合剂与晶圆具有不同的热胀冷缩特性,片内高温还会损害芯片封装的稳定性。同时,对功耗的控制还导致了堆叠MCP闪存无法使用更高性能(同样高能耗)的闪存晶片和控制器,也影响了堆叠MCP芯片的读写性能。

展望未来:NAND的后续继任者们

10年间,Flash改变了我们对于存储的认识。如果没有它的诞生和快速发展,我们现在可能还随身携带着丑陋的软盘或者可擦写光盘;曾经庞大的使用30GB硬盘的iPod怎么也无法变成现在小巧的iPod;更不会出现能够令SATA 3Gbps带宽也捉襟见肘的固态硬盘。但是Flash也有它的固有缺陷—由于写入数据前需要先擦除,使得Flash写入性能始终无法和读取速度同日而语。而且Flash寿命始终停留在百万次之内。于是当我们试图代替易失性SRAM和DRAM时,Flash不得不让位于未来更新的存储器件:铁电存储器(F-RAM)、相变存储器(PCM)和磁性存储器(MRAM)。

F-RAM通过分子内的原子位置来储存数据。当一个电场被加到铁电晶体时,中心原子顺着电场的方向在晶体里移动;当原子移动时,它通过一个能量壁垒,从而引起电荷击穿。

内部电路感应到电荷击穿并设置存储器。移去电场后,中心原子保持不动,存储器的状态也得以保存。铁电存储器不需要定时更新,掉电后数据能够继续保存,速度快而且不容易写坏。

PCM是基于材料的电致相变。相变材料可呈现晶态和非晶两种状态,分别代表了0和1,只需施加很小的复位电流就可以实现这两种状态的切换,完成数据写入。而读取时由于非晶体和晶体有着绝然不同的电阻,因此通过对比电流大小就能读出数据。

MRAM则是以磁性单元为基础,相当于在MRAM芯片中内置海量的磁性单元,每个单元对应一个微型磁头。通过微型磁头改变磁性单元的电阻存入数据,而读出数据也是通过判断单元电流大小。

这三种新技术的耐用性明显优于闪存,它们的写入次数可达1亿次以上,写入速度也比闪存快,而读取速度大体上与闪存相似。不过F-RAM的功耗显著低于闪存、PCM和MRAM,这对于功率预算非常低的应用来说是一个有利因素。不过和成熟的闪存比,这三种新技术目前还处于初级发展阶段,F-RAM已经商用多年,但是始终无法得到大规模采用。PCM、MRAM也已经量产,但是应用领域还赶不上F-RAM。加上存储容量和成本完全没有竞争力,短期内还不能替代闪存技术。而且三种技术之间也存在激烈竞争,今后闪存、内存退役时,存储市场谁执牛耳,我们拭目以待。